HBM4“改道”背后:混合键合为何暂别下一代高带宽内存?

本文来自微信公众号:歪睿老哥,作者:歪睿老哥,原文标题:《HBM4 突然“改道”:被寄予厚望的混合键合,为何临阵推迟?》

AI训练对高带宽内存的需求正呈爆发式增长,数据中心中数据搬运消耗了大部分能耗,而HBM(高带宽内存)凭借远快于普通DDR的传输速度和更低能耗,成为AI时代的核心内存方案。

此前行业普遍认为,下一代HBM4需采用混合键合技术才能实现16层堆叠,但JEDEC(固态技术协会)修改规则后,混合键合被推迟至下代——HBM4仍沿用微凸点方案,混合键合只是暂缓而非取消。本文将解析这一变化的来龙去脉。

1. 为何原计划HBM4必须采用混合键合?

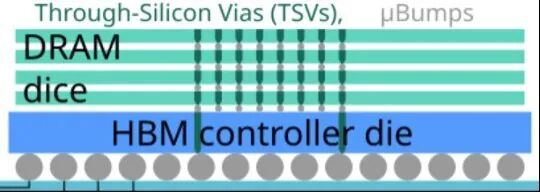

先梳理HBM的基本原理:HBM通过将多个内存裸片垂直堆叠,借助TSV(硅通孔)实现垂直连通,在相同面积下提升容量与带宽。

目前HBM已实现12层堆叠,若要升级至16层,此前JEDEC规定HBM模块最大高度不超过720微米,增加4层需压缩每层厚度及层间间隙。

裸片厚度已压缩至30-50微米,TSV间距缩小会带动微凸点(层间连通的焊接凸点)尺寸与高度同步减小,横向TSV间距缩小也会影响垂直堆叠总高度。原微凸点方案难以满足16层堆叠的空间需求,因此混合键合——无凸点的3D堆叠技术成为首选,它能消除层间间隙,在控制总高度的同时支持更多层堆叠。

混合键合本身优势显著,ASE集团工程总监Vikas Gupta指出,与微凸点方案相比,混合键合每比特能耗可降低一个数量级,性能与功耗表现更优,本就是HBM下一代技术的明确方向。

2. 混合键合为何推迟?成本与良率成关键瓶颈

技术方案虽优,但落地面临两大核心问题:工艺成本高、良率难保障。

首先,混合键合需全新设备,单颗封装成本远高于微凸点方案,即便单位比特成本因容量提升未大幅上涨,首发阶段的投入代价仍较大。

更棘手的是良率与测试环节:十几颗裸片堆叠时,只要一颗存在不可修复缺陷,整个堆叠就会报废,因此必须在堆叠前筛选出合格裸片(Known Good Die)以保证良率。

联电先进封装总监Pax Wang表示,微凸点方案可在焊接前测试每层内存,但混合键合的测试流程难度骤增。

第一个难题是混合键合要求键合界面绝对洁净,不能有任何颗粒,而探针测试本身会产生颗粒污染,还可能划伤焊盘表面。目前的解决思路是测试后增加平面化工序修复界面,这无疑增加了流程复杂度。

第二个难题是产业链流程调整:原流程中晶圆厂将裸片发给封测厂,封测厂测试后再堆叠;若晶圆厂自行堆叠,则需添置测试设备,整个产业链的协作模式需重新梳理,难以快速落地。

除测试外,过程中的检测监控也更复杂。yieldWerx CEO Aftkhar Aslam提到,当前已采用光学干涉、声学显微镜、在线微空洞检测等手段,还需建立垂直溯源体系,关联每颗裸片的晶圆批次、老化历史、键合对齐数据,以定位3D堆叠中的隐性缺陷,这套体系仍在完善中。

恰逢JEDEC将HBM模块高度限制从720微米放宽至775微米,为微凸点方案留出16层堆叠的空间,因此无需强行采用尚未成熟的混合键合技术。

3. HBM4的其他升级:不止于层数增加

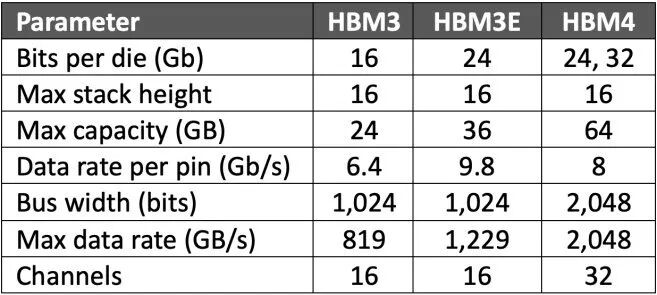

HBM4不仅实现16层堆叠,带宽与能效也有显著提升:通道数翻倍、接口更宽,每针信号速率快于HBM3、略低于HBM3E;容量提升后,每比特能耗降低30%-40%,这对AI降本增效至关重要。

还有两个逻辑层面的变化值得关注:

一是基底层(堆叠的逻辑底die)从通用规格转向可定制。此前HBM底die为统一标准,现在AMD、英伟达等大客户可定制底die功能,将部分处理器工作卸载到底die上以优化整体效率,同时市场仍保留通用款供普通厂商使用。

ASE的Gupta也指出,这种定制化会直接影响功耗、供电与热管理,需与整体计算架构协同进化。

二是安全与可靠性升级。HBM4加入Directed Refresh Management(DRFM,定向刷新管理)以防范行锤击打攻击,可针对受影响的存储行进行定向刷新,同时RAS(可靠性、可用性、可服务性)也全面优化。

通用高带宽存储器(HBM)结构

4. 混合键合只是暂缓,未来仍需依赖

当前HBM4的焊盘间距已达10微米,现有混合键合技术在该间距下无成本优势,加上JEDEC放宽高度限制,微凸点方案足以支撑需求,因此混合键合的量产被推迟。

这并不意味着混合键合被放弃,HBM4E或HBM5要实现18层甚至20层堆叠及更密集的互连,仍需依赖混合键合。目前HBM4预计2026年量产,HBM4E约2027年跟进,三星目标是HBM4E实现每针13Gb/s、总带宽3.25TB/s,功耗进一步降低。

行业也在探索混合方案:例如先将两个DRAM裸片面对面混合键合,再将成对裸片用微凸点背对背堆叠,既利用混合键合减少厚度,又避开全混合键合的难度,传统MR(回流焊)和TCB(热压键合)设备仍可沿用。

未来更高密度的堆叠,无论采用何种方案,都需要更精准的贴装设备、更稳定的超薄晶圆减薄材料,材料与设备的协同升级已在推进中。

行业普遍预期HBM5才会大规模应用混合键合,量产时间约在2030年前后,这为行业留出了打磨工艺、梳理产业链的时间,给内存产业提供了缓冲空间。

5. 总结

技术升级并非越新越好,而是成本、需求与产业链成熟度共同作用的结果。原本认为HBM4必须采用混合键合,但标准修改后,成熟的微凸点技术得以再支撑一代,既满足当前AI对容量与带宽的需求,又为下一代技术争取了完善时间,是务实的选择。

混合键合仍是HBM的未来方向,但在技术完全成熟前,将现有技术发挥到极致,才是对产业最有利的路径。

后续只需关注2026年HBM4的量产进展,以及HBM4E上混合键合能否顺利启动即可。

本文仅代表作者观点,版权归原创者所有,如需转载请在文中注明来源及作者名字。

免责声明:本文系转载编辑文章,仅作分享之用。如分享内容、图片侵犯到您的版权或非授权发布,请及时与我们联系进行审核处理或删除,您可以发送材料至邮箱:service@tojoy.com