0.2nm芯片路线图首次公布,未来20年逻辑技术节点持续演进

比利时半导体研发机构imec上月发布了一份研发路线图,详细阐述了2020年代至2040年代半导体制造技术的发展方向,并重点介绍了多项关键技术。

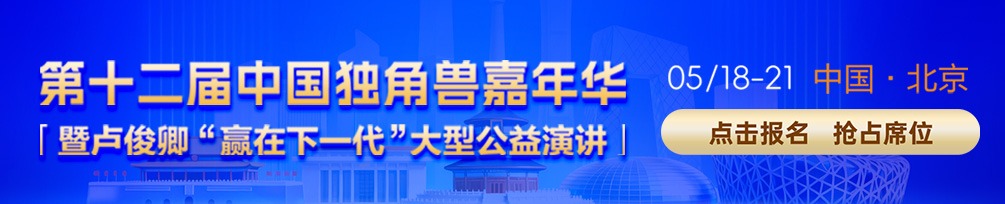

首先需要说明的是,水平小型化在2010年代后期已接近极限。SRAM单元面积每两年缩小一半(加工尺寸每两年缩小0.7倍)的趋势一直持续到2010年左右,之后放缓至每四年缩小一半,大致从2012年延续到2018年。

此外,尽管2020年以来技术节点不断进步,但SRAM单元面积基本保持稳定。标准6晶体管单元的最小面积仍在0.025平方微米至0.023平方微米之间。

1998年至2025年SRAM单元面积缩减趋势

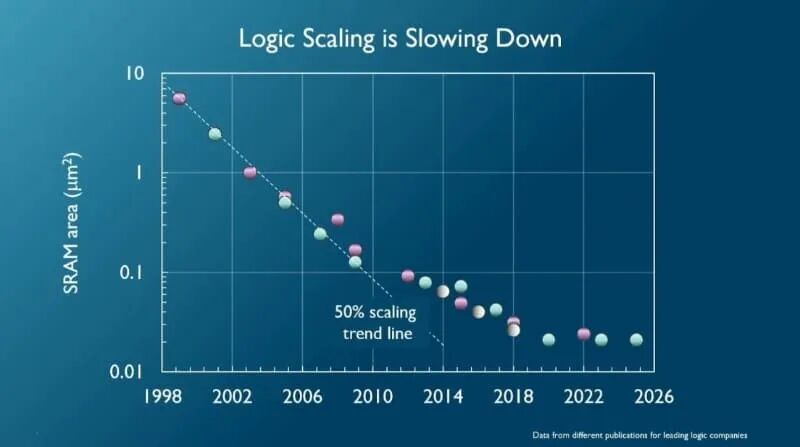

即便水平小型化已近极限,对半导体集成电路更高密度和性能的追求仍在继续。人工智能/高性能计算领域对高密度和高性能的需求依然旺盛。

因此,行业正通过“3D缩放”(兼顾水平与垂直方向)、在晶体管和布线中引入“新材料”以及“2.5/3D互连”技术等基础手段,推动半导体器件的密度提升与性能增强。同时,内存访问瓶颈、稳定供电难度加大、功耗急剧上升以及散热技术亟待升级等挑战,制约着人工智能/高性能计算系统性能的提升,不同技术的协同优化变得愈发重要。

提升系统性能及新型元素技术协同优化的挑战。左图展示新型元素技术,上图展示提升系统性能的挑战

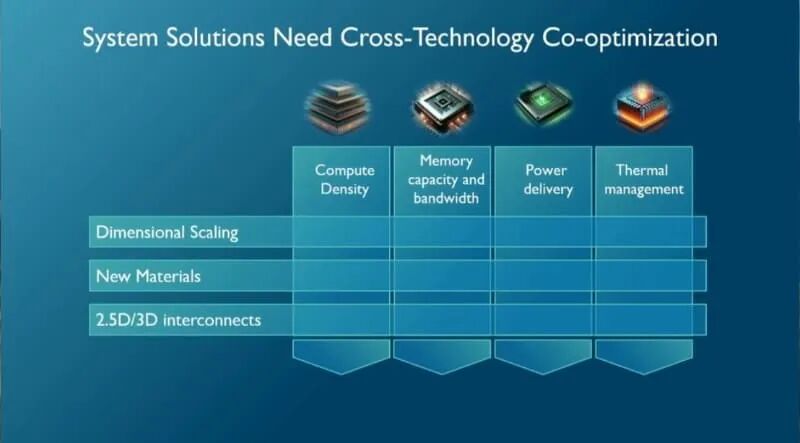

值得关注的是,本次路线图首次披露了2A(0.2nm)及sub-2A以下的芯片路线图。

未来20年,逻辑技术节点持续改进

imec认为,半导体逻辑器件的技术节点不仅会在2020年代持续发展,还将延续至2040年代。其报告展示的半导体逻辑器件技术节点跨越28年,从2018年量产的“N7(7纳米)节点”到2046年的“亚A2(小于2埃)节点”。以2026年为起点,技术节点的改进还将持续20年。埃(Å)是长度单位,为纳米的十分之一。

从场效应晶体管(FET)技术来看,2018年的N7节点、2020年的N5(5nm)节点以及2023年的N3(3nm)节点均采用FinFET技术。从2025年的N2节点开始,纳米片FET(又称GAA全栅场效应晶体管)被采用。imec预测,纳米片FET将进一步优化,应用于2028年的A14(1.4nm或14埃)节点和2031年的A10(1.0nm或10埃)节点。

随后,2034年工艺节点发展到A7(0.7纳米或7埃)时,场效应晶体管技术将被互补型场效应晶体管(CFET)取代。CFET是将p沟道纳米片FET和n沟道纳米片FET垂直堆叠的晶体管,理论上CMOS逻辑电路的晶体管密度预计可达纳米片FET的1.6至1.8倍。改进后的CFET将继续应用于2037年的A5(0.5纳米或5埃)工艺节点和2040年的A3(0.3纳米或3埃)工艺节点。

据预测,从2043年的“A2(0.2纳米或2埃)节点”开始,将采用“二维场效应晶体管(2D FET)”,其中CFET的纳米片状沟道材料将被“二维材料”替代。2D FET也将应用于2046年的“A2以下节点”。

2018年至2046年半导体逻辑技术路线图。该路线图涵盖场效应晶体管技术和晶圆背面元件技术

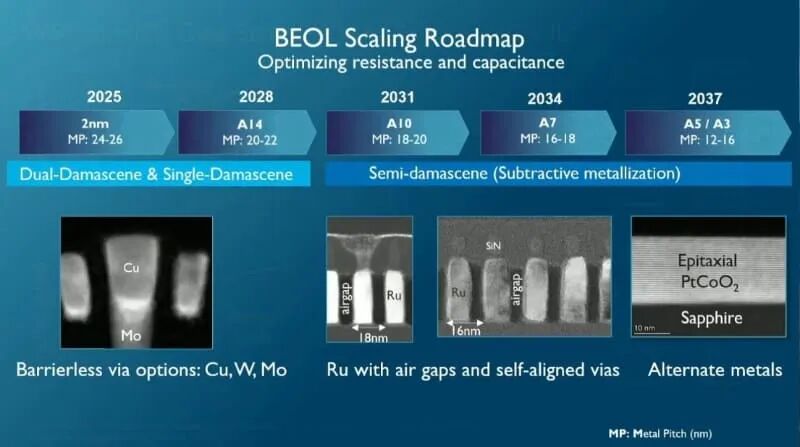

2025-2037年布线技术路线图

在半导体晶圆上制造大规模逻辑电路的过程大致分为前端工艺(FEOL)和后端工艺(BEOL)。前端工艺负责制造晶体管,后端工艺则负责制造多层布线。通常,连接晶体管的布线(多层布线)在晶体管制造完成后形成,因此工艺顺序为先前端工艺,再后端工艺。

前文提到的路线图主要列出了前端工艺开发的晶体管技术及其对应的工艺节点。imec在报告中也展示了后端工艺路线图,其时间范围比前端工艺路线图窄,从2025年的2nm节点(N2节点)延伸至2037年的A5/A3节点。

2025年N2节点的布线技术最小间距为24nm至26nm,采用铜(Cu)作为布线金属,运用双镶嵌和单镶嵌工艺。下一代节点即2028年的A14节点,最小间距将缩小至20nm至22nm,这主要通过对N2节点的改进实现。

到2031年的A10节点,最小布线间距将进一步缩小至18nm至20nm。钌(Ru)是布线金属的热门候选材料,空气间隙是相邻布线间绝缘的热门选择。采用钌布线时,布线成型技术将转变为减材制造法,过孔(连接各层的孔)的加工将采用自对准技术。

2034年的A7节点旨在将最小间距缩小至16nm-18nm,这将通过改进钌金属、空气间隙和自对准通孔技术实现。2037年的A5节点旨在进一步将最小布线间距缩小至12nm-16nm,实现该目标的技术仍在研发中。

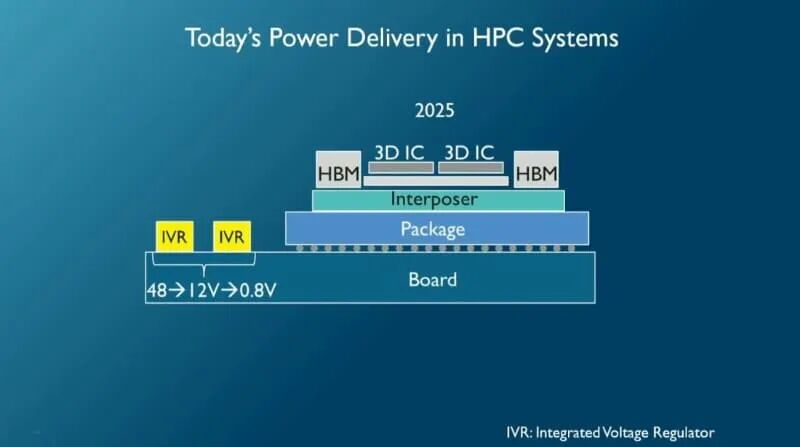

2025-2032年电源技术路线图

imec还概述了对高性能计算(HPC)先进封装电路板电源技术的未来展望。目前的电源技术是在印刷电路板表面安装多个集成电压调节器(IVR)模块,将电源电压从48V直流降至12V直流,再进一步降至0.8V直流。

目前高性能计算(HPC)的电源技术,多个集成恒压电路模块安装在电路板表面

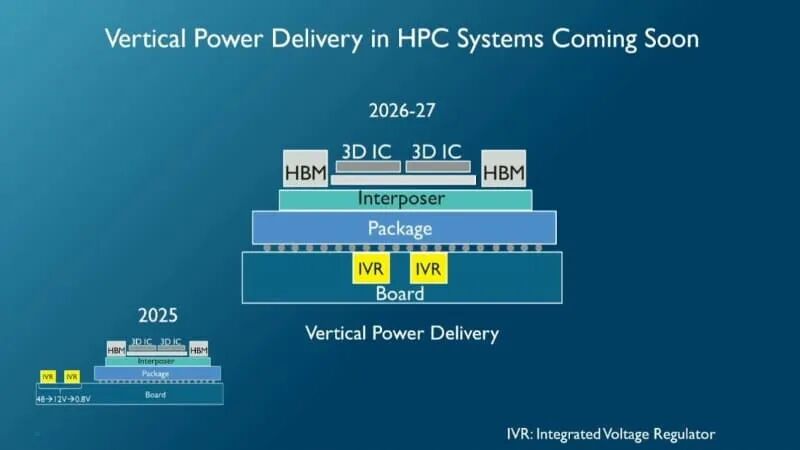

2026年至2027年间,将出现一种新型电源技术,可将多个集成电压调节器(IVR)系统集成到电路板内部。这将缩小电路板面积,缩短IVR与半导体芯片(3D IC和HBM)之间的距离。电源电路电阻和电容的降低有望提高电源效率并抑制噪声。

下一代高性能计算电源技术预计将于2026-2027年问世,IVR系统已集成在电路板中

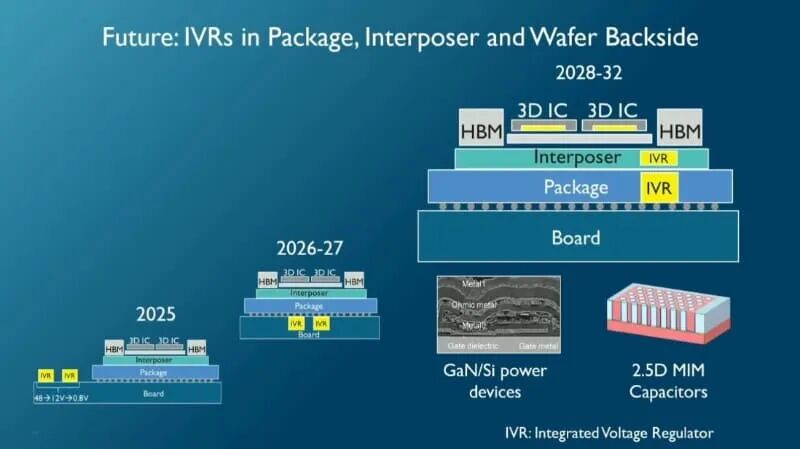

未来,集成电压调节器(IVR)将被嵌入封装基板、中间基板(中介层)以及半导体芯片的背面(3D IC)。预计采用此类下一代电源技术的高性能计算模块将在2028年至2032年间实现。此外,为提高效率并降低噪声,可能会采用基于硅(Si)上氮化镓(GaN)技术的功率器件单片集成技术,以及采用金属、高介电常数绝缘膜和金属的2.5D高容量MIM电容器技术。

下一代高性能计算电源架构预计将于2028年至2032年间出现(上图)以及新的基础技术

背面供电网络(BS-PDN)散热量减少

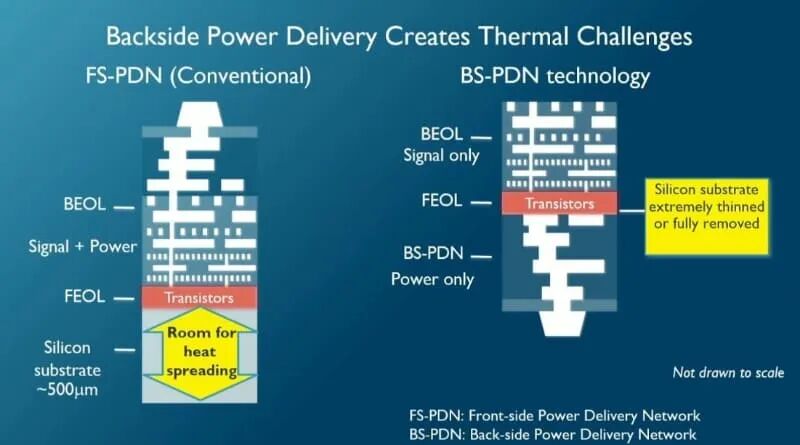

2028年至2032年间,备受关注的电源技术是用于硅芯片的“背面供电网络(BS-PDN)”技术。传统上,信号线和电源线(包括接地线)都布置在晶圆正面,为与BS-PDN区分,这种布置方式被称为“正面供电网络(FS-PDN)”。

在传统FS-PDN技术中,信号线和电源线混杂在表面。电源线的最大电流远高于信号线,信号线可通过水平微型化变细,但电源线因电流密度增加会导致电迁移影响寿命,不能做得过细,这限制了信号线的布局。

传统供电网络(FS-PDN,左)和下一代供电网络(BS-PDN,右)的布线结构

因此,BS-PDN将电源网络移至背面,正面仅包含信号布线层,简化了布局并提高了信号布线密度。

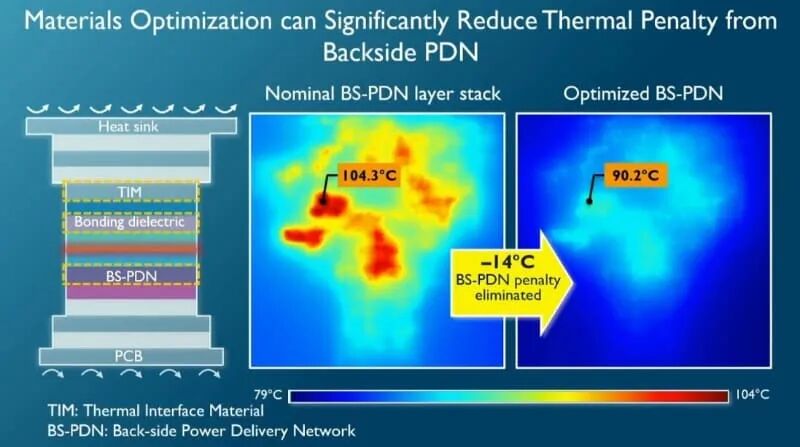

BS-PDN的缺点是散热性能显著下降。在FS-PDN中,背面的电路板起到散热通道作用;而在BS-PDN中,除电源线外背面厚度可忽略,移除电源线后散热通道消失,导致散热能力下降。

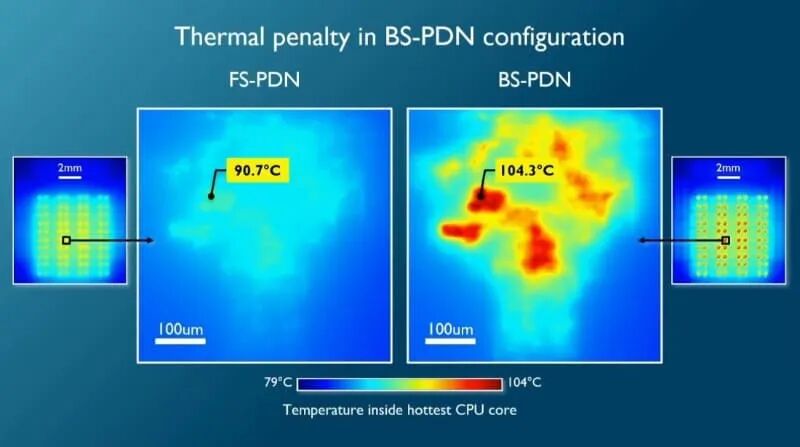

对比CPU核心阵列的最高工作温度,FS-PDN保持在90.7°C,BS-PDN则升至104.3°C,温度升高了近14°C。

CPU核心阵列最高工作温度对比。左图为传统供电网络(FS-PDN),右图为后置供电网络(BS-PDN)

提高背面供电网络(BS-PDN)的散热性能

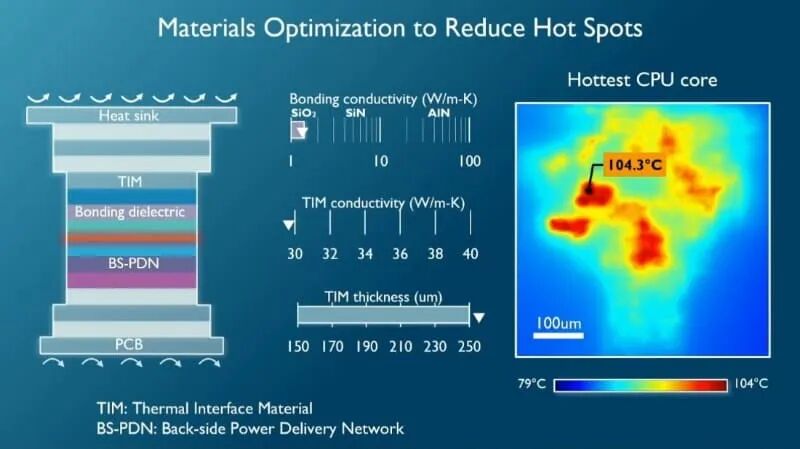

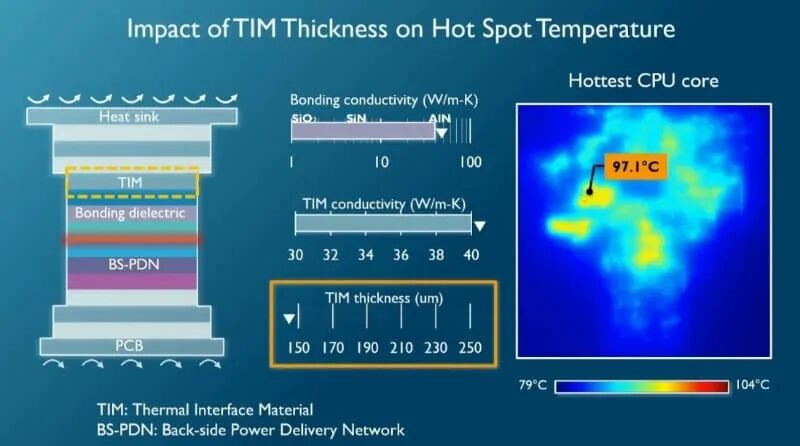

为此,行业尝试提升散热性能:将连接前后表面的介电材料更换为高导热材料,导热界面材料(TIM)也更换为高导热材料,同时减小TIM的厚度。通过这些措施,最高温度降至97.1°C。

背部供电网络(BS-PDN)的结构。在采取散热措施之前(最高温度104.3°C)

具体而言,将结处的介电材料从传统二氧化硅更换为氮化铝,导热系数提高了40倍;导热界面材料的导热系数提高了1.33倍,厚度减少到原厚度的60%。

背部供电网络(BS-PDN)结构,实施散热措施后的状态(最高温度97.1°C)

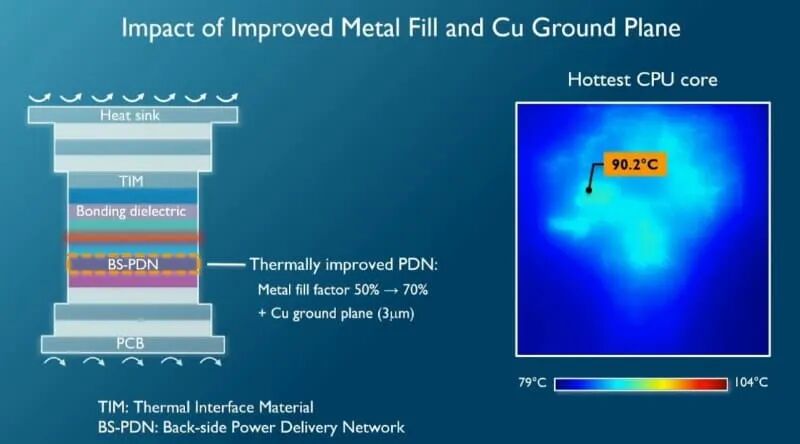

此外,背部供电网络的金属化程度从传统的50%提高到70%,并增加了一层厚度为3μm的铜接地层,最高温度因此降低至90.2°C。通过这些措施,最终温度低于FS-PDN的最高温度90.7°C。

这一结果归功于对背部供电网络本身的改进(最高温度90.2°C)

背部供电网络散热措施效果总结:措施实施前温度为104.3°C,实施后温度降至90.2°C,降幅约为14°C

当然,这些散热措施会导致成本增加,批量生产中找到平衡点至关重要。

本文来自微信公众号“半导体行业观察”(ID:icbank),作者:imec,36氪经授权发布。

本文仅代表作者观点,版权归原创者所有,如需转载请在文中注明来源及作者名字。

免责声明:本文系转载编辑文章,仅作分享之用。如分享内容、图片侵犯到您的版权或非授权发布,请及时与我们联系进行审核处理或删除,您可以发送材料至邮箱:service@tojoy.com