台积电CFET技术获重大突破:从器件到电路集成的关键跨越

在2025年国际电子器件会议(IEDM)上,台积电首次展示了基于互补场效应晶体管(CFET)技术的集成电路运行成果,标志着该技术从器件级优化迈向电路级集成的关键性转变。

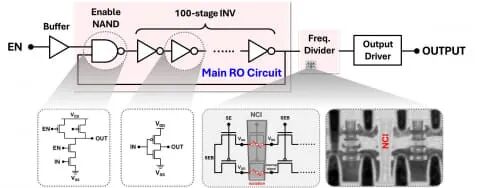

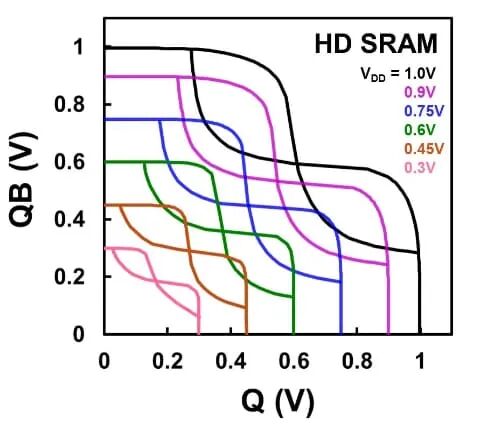

根据IEDM官方预告,台积电此次公布两项里程碑成果:首款全功能101级3D单片CFET环形振荡器(RO),以及全球最小的6T SRAM位单元,该单元同时实现高密度与高电流设计。

基于此前纳米片单片CFET工艺架构,台积电团队引入多项创新集成技术:将栅极间距缩小至48nm以下,采用纳米片切割隔离(NCI)技术实现相邻FET隔离,在6T SRAM位单元中通过对接接触(BCT)互连技术完成反相器交叉耦合。电学分析对比两种环形振荡器布局,重点验证了6T位单元对性能及SRAM器件稳定性的影响。

台积电CFET技术新进展

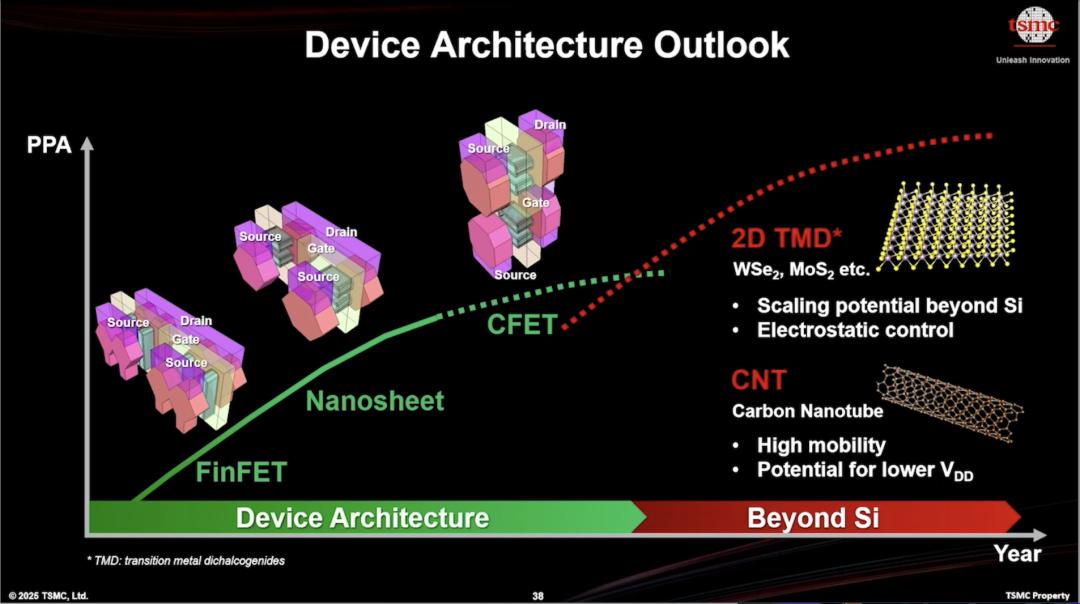

CFET通过垂直堆叠n沟道与p沟道FET(CMOS核心组件)提升晶体管密度,理论上比当前先进纳米片FET密度提升近一倍。但技术难度极高:纳米片FET制造已极具挑战,而CFET需将其单片垂直堆叠,工艺复杂度进一步增加。此前CFET研发多限于器件级,去年IEDM上台积电曾展示CFET反相器原型,此次则实现电路级集成突破。

台积电研发团队制作了两类集成电路原型:逻辑电路基础的环形振荡器,以及存储电路核心的SRAM单元。其中环形振荡器规模达800-1000个晶体管,由使能NAND元件与100个反相器组成101级结构,工作电压范围0.5V-0.95V,电压升高时振荡频率提升、波动减小。

SRAM单元采用6晶体管配置,分为高密度(HD)型与高电流(HC)型,均验证可正常工作。HD型面积比同设计规则纳米片FET单元小30%,比HC型小20%;HC型读取电流为HD型1.7倍。HD型工作电压0.3V-1.0V,0.75V时读取静态噪声容限(RSNM)135mV、读取电流17.5μA、写入容限(WM)265mV,参数仍有优化空间。SRAM的交叉耦合结构需通过BCT接触点实现上下FET互连。

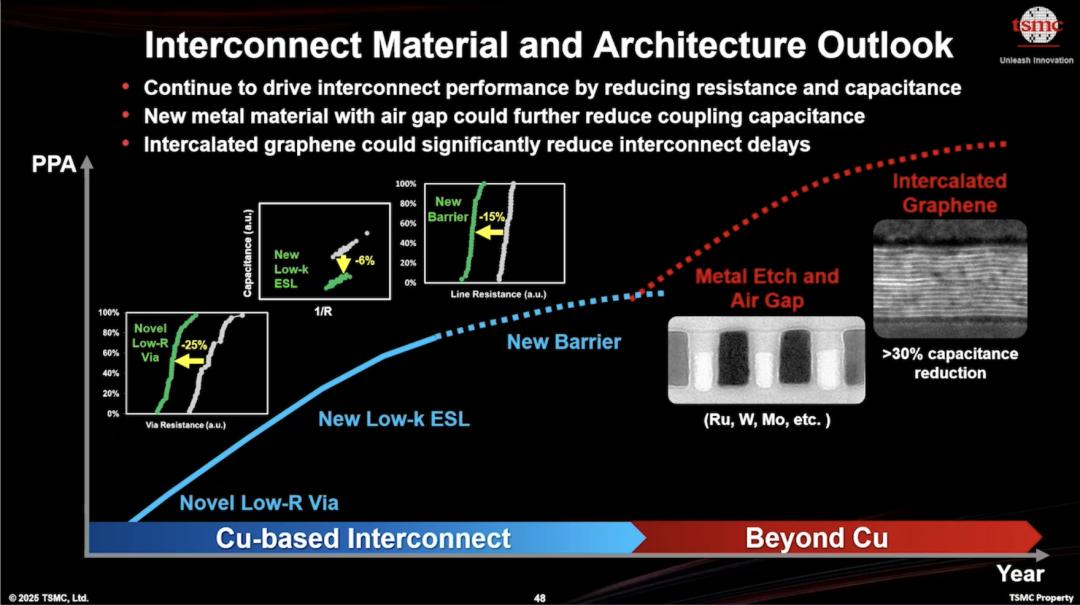

此外,台积电在二维沟道材料晶体管领域也有进展,展示了类似N2技术的堆叠纳米片单层沟道晶体管电性能,及匹配良好的N/P沟道器件组成的1V工作反相器。未来还计划研发新型互连技术,包括铜互连的过孔方案优化、新型阻挡层,以及气隙金属材料、插层石墨烯等,以降低电阻与耦合电容。

全球芯片巨头CFET布局

三星、英特尔等企业也在积极推进CFET研发:

英特尔是最早展示CFET的厂商,2020年IEDM发布早期版本,2023年推出改进型反相器。其采用背面供电技术,允许硅片上下同时布置互连线,简化底部晶体管连接,实现60nm接触多晶硅间距(CPP)的反相器,尺寸仅为传统CMOS反相器的50%。

三星展示了48nm与45nm CPP的CFET器件(英特尔为60nm),虽为单个器件而非完整反相器,但较小尺寸原型性能下降幅度可控,团队认为可通过工艺优化解决。三星采用干法刻蚀替代湿法刻蚀实现源漏隔离,良率提升80%,并通过底部接触方式节省空间,每个成对器件使用单个纳米片(英特尔为三个),研究人员称增加纳米片数量可提升性能。2024年IEDM上,三星与IBM研究院联合展示阶梯式沟道设计的单片堆叠FET,通过下层宽沟道降低堆叠高度,缓解高纵横比制造挑战。

CFET:半导体微缩的必经之路

行业专家认为,在CFET普及前,纳米片架构将经历三代发展,期间CMOS元件(如SRAM)尺寸缩小可能停滞。比利时微电子研究中心(imec)预测,2032年工艺节点微缩速度放缓,将迫使行业依赖芯粒与先进封装技术,而CFET是继续实现逻辑电路与SRAM微缩的关键路径,有望超越1纳米节点。

不过CFET商业化仍面临挑战:供电架构设计复杂,高纵横比结构增加制造难度,可能导致工艺复杂度与成本上升。台积电强调,需谨慎选择集成方案以降低复杂度,减少新材料与工艺需求,并尽早开展EDA工具开发以应对设计变更。

尽管CFET技术潜力巨大,但仍需时间突破技术瓶颈,预计2030年代才能实现逻辑与存储领域的实际应用。

本文来自微信公众号“半导体行业观察”(ID:icbank),作者:编辑部,36氪经授权发布。

本文仅代表作者观点,版权归原创者所有,如需转载请在文中注明来源及作者名字。

免责声明:本文系转载编辑文章,仅作分享之用。如分享内容、图片侵犯到您的版权或非授权发布,请及时与我们联系进行审核处理或删除,您可以发送材料至邮箱:service@tojoy.com