RISC-V架构成主流,验证环节价值突显

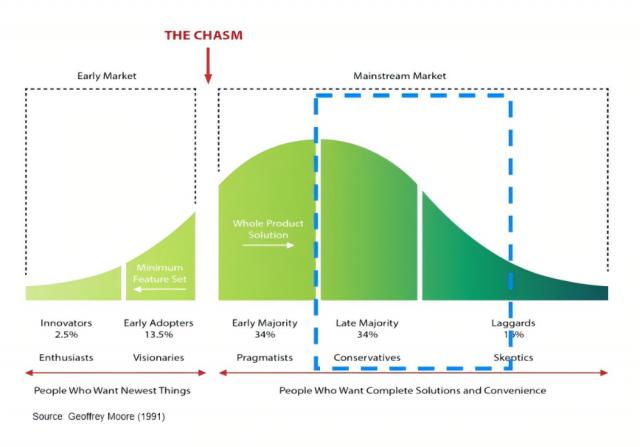

电子发烧友网报道(文 / 吴子鹏)从私有架构走向开放架构的浪潮,正深刻影响着全球半导体产业。RISC-V作为一种开放的指令集架构(ISA),凭借开放性和模块化设计,为开发者带来前所未有的自由度与灵活性,正从早期采用者阶段迈向主流市场。

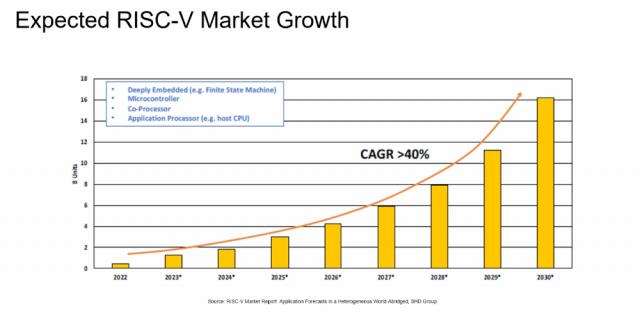

据咨询公司SHD Group研究数据,2024年全球RISC-V芯片出货量超18亿颗,2030年将突破160亿颗,年复合增长率超40%。如今,几乎所有半导体厂商都有在研的RISC-V芯片项目,超大规模企业、汽车OEM及一级供应商等也积极参与。不过,RISC-V的定制化优势也给验证领域带来新课题:如何在满足多样化设计需求时,确保芯片质量达业界标杆水平。为此,新思科技(Synopsys)经七年多RISC-V验证实践,总结出完整验证方法论,助力行业应对挑战。

RISC-V的价值与挑战

RISC-V的模块化ISA让开发者可按需添加或去除功能,打造适配特定应用场景的处理器。这使物联网微控制器(MCU)、AI专用加速器、高性能应用处理器(CPU)等,能在ISA与微架构层面深度定制,构建“领域专属处理器”,形成业务差异化优势。

这种创新模式技术灵活性高,重塑了产业链成本结构与创新节奏。以芯片创新为例,过去十多年,SoC差异化围绕主频、制程、外围接口等,如今RISC-V的模块化ISA将差异化创新从封装层面拉回内核层面,让内核成技术壁垒。

从商业角度看,RISC-V的模块化ISA使CPU设计回归“菜单点菜”模式,即“搭乐高式”芯片设计。而传统架构(x86/ARM)是“套餐”模式,手机SoC或车载MCU都要为可能用不到的浮点运算、SIMD等特性付费。

然而,随着RISC-V普及,验证挑战日益突出。RISC-V芯片验证面临设计复杂性、资源限制及验证效率等难题,具体如下:

难题一:设计源头与场景的多样性

RISC-V芯片设计源头可能是自研、开源RTL或供应商授权IP,部分场景还需添加自定义指令。若面向外部软件开发,还需验证边角案例,以揭示系统极限状况下的性能和稳定性。

难题二:用户与开发者的质量预期偏差

终端用户期望RISC-V芯片质量对标基于ARM架构的芯片,后者需10¹⁵次验证周期确保稳定性。但多数RISC-V芯片开发者面临专业能力、验证方法论与资源的三重缺口,难以弥合质量鸿沟。

难题三:团队经验的适配难题

多数验证工程师擅长SoC级验证,缺乏处理器全面验证经验。处理器验证对参考模型质量和功能完整性要求更高,设计团队需深度参与验证流程,高效协同成为项目落地关键挑战。

RISC-V全面验证价值凸显

可见,RISC-V生态中,处理器IP开发者与终端用户存在“验证认知偏差”。其开放性、模块化和可定制化加剧了状态空间复杂性,带来验证挑战。解决这些问题需完善的验证计划,整合动态与形式化验证技术,覆盖所有指令组合和状态转换,确保芯片在复杂场景下的可靠性。

全面验证方法从技术、应用、生态三大维度赋能RISC-V发展。一是应对架构复杂性,弥补开源生态质量缺口,通过标准化流程和硅验证工具链,确保设计规范和硬件可靠性,提升验证效率、缩短开发周期。二是保障安全与功能正确性,借助功能覆盖率和形式化验证工具,保障功能安全与信息安全。三是在生态层面,提升各行业使用RISC-V芯片的信心,促进产业繁荣。

新思科技提供一站式RISC-V验证解决方案

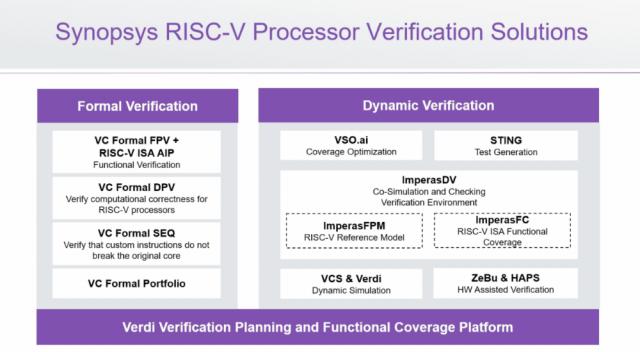

作为多领域核心技术驱动者,新思科技在RISC-V验证领域领先,构建了覆盖形式化与动态验证的完整方案。

形式化验证:为RISC-V设计提供全面分析和调试技术

形式化验证用数学逻辑证明设计是否符合规范,无需依赖测试用例。新思科技的VC Formal是主流工具,集成多种设计与验证解决方案。针对RISC-V处理器单元设计特性,其核心能力包括:属性验证(FPV)检查设计功能属性;时序等效性检查(SEQ)对比设计时序逻辑行为;数据路径验证(DPV)验证数据运算与传输路径功能;寄存器验证(FRV)验证配置寄存器行为;安全验证(FSV)确保安全数据流向和完整性。新思科技提供完整RISC-V断言IP库,用户可直接调用,缩短验证启动时间。

动态验证:让RISC-V庞大的状态空间不再棘手

RISC-V开放标准使设计人员可自由设计扩展处理器,但导致状态空间膨胀。动态验证模拟实际运行场景,确保处理器功能正确。新思科技提供ImperasDV协同仿真环境、STING测试生成工具等,还可借助AI助手VSO.ai加速验证。ImperasDV是核心平台,采用“RTL与参考模型并行仿真 + 实时状态对比”,覆盖状态空间,提供锁步比较设计验证方法,与其他工具无缝集成,提升效率。ImperasFC提供自动化功能覆盖,解决传统动态验证问题。STING是随机自检测试生成器,支持多核架构,可配置系统参数,加速验证,提供多样化测试开发机制,支持“左移”验证流程,减少重复开发工作量。

综上,新思科技的RISC-V验证方案通过“动态 + 形式化”技术整合,为开发者提供可落地、高可靠的验证路径,解决核心痛点,支撑生态多元化扩张,成为推动开放架构在各垂直领域落地的关键基础设施。

本文仅代表作者观点,版权归原创者所有,如需转载请在文中注明来源及作者名字。

免责声明:本文系转载编辑文章,仅作分享之用。如分享内容、图片侵犯到您的版权或非授权发布,请及时与我们联系进行审核处理或删除,您可以发送材料至邮箱:service@tojoy.com