突破 AI 算力困境:3D - IC 技术架构的变革性创新

以下文章来自 Cadence 楷登,作者 Cadence

AI 时代的数据洪流与算力瓶颈

从日常语音助手、自动驾驶,到工业全自动工厂、AI 辅助设计,人工智能正给世界带来变革。在 AI 应用里,文字、语音、视频等都要转化为基本数据单元(token),供 AI 处理器识别运算。

现代 AI 系统常面临海量 token 输入,需在一秒内处理十亿甚至百亿级 token。这种高并发、高带宽需求对计算机架构和芯片设计提出挑战。传统二维芯片,尤其是采用冯·诺伊曼结构的计算机,处理器与内存间的总线数据传输速率和带宽有限,无法承载 AI 时代的数据洪流。数据显示,当前 AI 芯片算力利用率通常低于 30%,主要原因是处理器与内存间的数据传输速率和带宽跟不上运算速度。这种“内存墙”现象已成为限制 AI 系统性能的瓶颈。

3D - IC ——突破维度的技术革命

为解决“内存墙”问题,主流 AI 芯片多采用 2.5D 设计制造。2.5D 是将存储和运算芯片放在同一平面,借助中介层传输芯片实现大量连接,初步解决了存储和运算间的数据通路拥塞问题。

此外,将大芯片切分为小的存储和运算芯片,可大幅提升良品率。但要满足更严苛的高并发、高带宽需求,需升级到 3D 设计,将存储芯片堆叠在运算芯片之上。

在 3D - IC 工艺中,金属微凸块或复合键可直接连接上下堆叠的芯片。若信号需穿过芯片,可通过硅通孔穿过硅衬底、器件层和金属层。3D - IC 结构下的芯片间垂直互连缩短了数据传输距离,提高了传输速率,降低了功耗。由于芯片整个接触面都可设置连接接口,芯片间并行连接数量大幅增加,带宽显著提高。这种将内存和运算结合的近存运算,是打破“内存墙”的重要手段。

先进的芯片设计者会根据运算需求,平衡性能和成本,采用 2.5D 和 3D 连接技术,即 3.5D 芯片。3.5D 设计能更好地支持异构运算和处理海量数据。

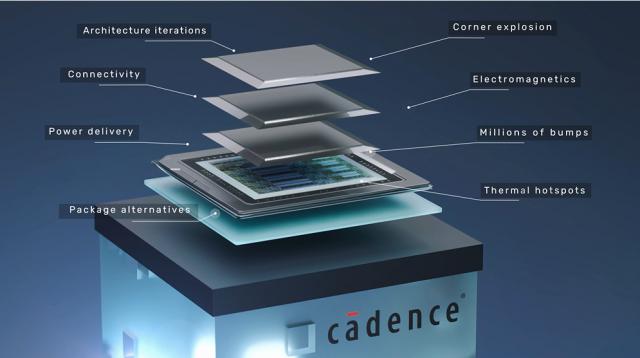

Cadence Integrity 3D - IC ——全流程设计平台

3D - IC 设计不同于传统封装和芯片设计,需要创新方法学和工具支持。传统先进封装流程先由封装确定芯粒接口,再拆分设计目标给芯片团队,无法实现系统级优化。3D - IC 设计需将传统 2D 芯片的性能、功耗、面积、成本指标驱动的设计拓展到 3D 系统。

Cadence 致力于提供软硬件和 IP 产品,推动电子设计落地。为此,Cadence 率先推出能在单一平台实现 3D - IC 全流程的 EDA 软件——Integrity 3D - IC,为业界提供了完整的 3D - IC 解决方案。该方案支持所有 3D - IC 设计类型和工艺节点,让 3D - IC 设计各部门通过 Cadence 的数字设计平台 Innovus、模拟及定制化设计平台 Virtuoso和封装与板级设计平台 Allegro实现全系统跨平台无缝协作。为达到更好的 3D 系统设计效果,Integrity 3D - IC 将设计流程分为:

早期架构探索 – 分析不同 3D 堆叠架构,快速迭代方案,优化 bump 和 TSV 的规划与摆放。

中期设计实现 – 进行 3D 系统的 partition 与 floorplanning、3D placement、CTS、routing 及优化,完成跨芯片的静态时序分析与收敛。

后期多物理场签核 – 包括对 3D - IC 签核至关重要的系统级热分析、电源分配网络分析、3D 系统的信号完整性与电源完整性、3D 静态时序分析等多物理场签核,以及系统级的 LVS 和 DRC。

这样能使 3D - IC 芯片的堆叠、互联及各芯粒根据全系统 PPAC 的最优或次优解规划实现,让芯片公司设计出更具竞争力的 3D - IC 产品。

未来展望:3.5D 异构集成时代

在半导体产业发展的关键节点,Cadence 积极探索行业前沿。面向未来,Cadence 愿与合作伙伴共同推动下一代 3.5D 技术创新。这不仅是技术参数的升级,更是对芯片设计方法学的重塑,为行业发展注入新动力。

释放你的想象,与 Cadence 携手,将创意变为现实!

有奖互动

点赞前沿科技,就有机会获得 20 份精美礼品!

现在,为我们的 3D - IC 科普视频点赞(见下方),并在“Cadence 楷登”公众号原文留言(点击此处前往),就有机会赢取好礼!活动结束后,视频号点赞 ( ❤️ ) + 公众号留言点赞最高的前 20 名朋友,将获得精美礼品。

▲ 点击观看视频

别错过机会!用点赞和留言连接创新与幸运,快来参与!

Cadence 定制款快充充电宝(价值约 115 元)

* 活动对象:全体“Cadence 楷登”公众号关注者

* 活动时间:本篇文章发布之日起至 2025 年 7 月 31 日 12:00 止

* 活动须知:请前往 Cadence 楷登订阅号参与相关活动。参与活动即代表同意活动规则,同意我们获取和使用您的微信昵称等信息,并同意事后就活动获奖等事宜与您联系。

兑奖规则

● 获奖者名单将于 2025 年 8 月中旬在微信公众号“Cadence 楷登”发文公布。

● 获奖者需保持微信畅通,工作人员将在获奖名单公布后十(10)个工作日内(“兑奖时间”)通过微信联系确认邮寄地址。若在兑奖时间内尝试三(3)次无法联系到您,将视为您主动放弃获奖资格。

● 符合规则的获奖者按规则获得奖品,活动参与者只能获奖一次。

● 获奖者兑奖需向“Cadence 楷登”微信公众号发送 “带 Cadence 账号留言的评论截图 + 视频号点赞截图”。

●为寄送奖品,需您提供准确、真实、完整的姓名、联系电话、联系地址等信息。若未能在兑奖时间内提供或信息有误导致奖品无法配送,将视为您主动放弃获奖资格。

● 我们将邮寄奖品,因交通管控等原因配送可能延迟,请耐心等待。

● 若对活动规则有疑问,请向邮箱 Digital - Marketing - China@cadence.com 发送邮件咨询。

(上下滑动查看更多)

欲了解更多 Cadence 3D - IC 精彩内容,

本文仅代表作者观点,版权归原创者所有,如需转载请在文中注明来源及作者名字。

免责声明:本文系转载编辑文章,仅作分享之用。如分享内容、图片侵犯到您的版权或非授权发布,请及时与我们联系进行审核处理或删除,您可以发送材料至邮箱:service@tojoy.com